UM12212

UM12212

S32K396-BGA-DC1

Rev. 1.0 – 3. února 2025

Uživatelská příručka

Informace o dokumentu

| Informace | Obsah |

| Klíčová slova | S32K396, EVB, Uživatelská příručka |

| Abstraktní | Informace potřebné pro práci s S32K396-BGA EVB |

Zavedení

Tento dokument popisuje vlastnosti zkušební desky S32K396 289MapBGA (EVB). Poskytuje vývojářům návod, jak by se deska měla používat, a popisuje její vlastnosti.

Řada mikrokontrolérů S32K396 zahrnuje S32K36x, S32K37x a S32K39x. Mikrokontroléry S32K39 rozšiřují vysoce výkonné možnosti mikrokontroléru S32K37 o dva programovatelné koprocesory pro řízení motoru a rozšířené analogové funkce. S32K396 se v tomto dokumentu používá k pokrytí všech variant mikrokontroléru.

Tato dceřiná karta (DC) S32K396 289MapBGA je schopna samostatného provozu a lze ji rozšířit o základní desku (MB) S32X-MB, která je běžná i pro řadu S32Z/E. MB poskytuje další zdroj napájení pro mikrokontrolér S32K396 a také rozšiřuje funkčnost karty DC o více fyzických rozhraní a uživatelských konektorů. Obě desky jsou připojeny pomocí odpovídajících konektorů (MB-DC).

S32K396 DC EVB přesview

Dceřiná karta je osazena několika komunikačními rozhraními, uživatelskými LED diodami, tlačítky a konektory (viz tabulka 1). Je povoleno několik možností pro ladicí rozhraní. JTAG je nakonfigurováno jako výchozí ladicí rozhraní.

Kromě toho jsou povolena také rozhraní OpenSDA a Trace. DC karta podporuje jedno rozhraní pro řízení motoru a konektor pro připojení EVB s Ethernet PHY. Jsou také podporovány tři další možnosti napájení pro všechny domény. EVB lze použít samostatně, kde je napájení zajištěno z 12V válcového konektoru a dále je zajištěno PMIC FS26, nebo lze napájení připojit nezávisle pomocí šroubovacího konektoru. V případě použití MB k rozšíření funkčnosti DC karty lze napájení generovat z regulátorů na desce MB.

Dceřiná karta (DC) je schopna samostatného provozu a její funkčnost lze rozšířit pomocí základní desky (MB). Obě desky jsou propojeny pomocí odpovídajících konektorů (MB-DC).

Tabulka 1. Více nežview Rozhraní S32K396 EVB

Tabulka 1. Více nežview Rozhraní S32K396 EVB

| Rozhraní | S32K396-BGA-DC1 | S32X-MB |

| CAN | 1x PHY (CAN0) | 4x PHY (CAN0, CAN1, CAN3, CAN4) |

| LIN | 2x převodník UART na LIN (UART2, UART3) | 2x převodník UART na LIN (UART2, UART3) |

| Ethernet | 1x konektor (bez PHY) | – |

| USB/UART | 2x (UART2, UART0) | 1x (UART 1) |

| MC konektor | 1x | 1x |

| Zipline | 1x | – |

| QSPI | 1x | – |

| MSC | 1x (záhlaví – LPUART_MSC, DSPI) | – |

| I2C | 2x (1x USB sériový port: I2C0, 1x konektor: I2C1) | – |

| FlexIO | Záhlaví | – |

| eMIOS | Záhlaví | – |

| Uživatelská LED | 3x (PTD4, PTD5, PTH7) | 4x |

| Uživatelské tlačítko | 4x (PTE21, PTG0, PTG1, PTG2) | 4x |

| Potenciometr | – | 1x |

| BMS rozhraní | 1× konektor (J59, LPSPI2, LPSPI3) | – |

Start-up

3.1 Konfigurace režimu PMIC

FS26 podporuje dva provozní režimy, Normální a Ladicí, založené na konfiguraci propojek (konfiguraci propojek viz Tabulka 2). Je-li vybrán Normální režim, je watchdog FS26 aktivní a pokud není včas obsloužen, resetuje S32K396 vysláním signálu RESET_b. Na základě konfigurace FS26 po několika resetech FS26 přestane generovat napájení MCU.

Tabulka 2. Výběr režimu FS26

| Režim FS26 | J10 | J11 |

| Normální | OTEVŘENO | Krátký |

| Ladění (výchozí) | Krátký | OTEVŘENO |

3.2 Zapněte napájení

Pro napájení desky pomocí externího 12V adaptéru postupujte takto:

- Při vybalování S32K396-BGA-DC1 dodržujte standardní postup ESD.

- Ujistěte se, že propojky pro rozvod napájení a napájení MCU jsou správně nakonfigurovány podle zamýšleného schématu napájení.

- Nakonfigurujte J4 (5.0 V), J7 (3.3 V) a J6 (1.5 V) tak, aby napájely z PMIC (pozice 2-4).

- Před připojením 12V napájení k EVB připojte potřebné kabely mezi hostitelským počítačem a EVB.

- Připojte EVB k napájení 12 V a přepněte přepínač SW10 do polohy ON (pravý → levý).

- Po připojení napájení k DC kartě čtyři zelené LED diody indikují přítomnost napájecího napětí.tages takto:

• LED D4 indikuje, že je napájení 12.0 V správně připojeno k stejnosměrnému proudu.

• LED D3 indikuje, že je napájení VCC_5V0 zapnuto.

• LED D2 indikuje, že je napájení VCC_3V3 zapnuto.

• LED D1 indikuje, že je zapnuto napájení 1.5 V.

Napájení

Existují tři způsoby, jak lze EVB dodat:

- Externí napájecí zdroj 12V/2A

– PMIC FS26 generuje veškeré potřebné napájení:

– Napájení VCC_5V0 pro analogové a digitální I/O (LDO2OUT)

– Napájení VCC_3V3 pro digitální I/O (LDO1OUT)

– Napájení 1.5 V pro generování 1.1 V pro jádro a logiku (CORE)

– VREF – napájení 5V pro analogové reference (VREF) - Externí napájecí zdroje 5.0 V, 3.3 V a 1.5 V přes šroubovací konektory [výchozí]

- Z hlavního měniče (12.0 V, 5.0 V, 3.3 V, 1.5 V)

![]()

4.1 Hlavní napájení 12 V pro EVB

Hlavní napájení pro dceřinou kartu 12 V může být napájeno buď z konektorů MB nebo DC. Pro distribuci 12V napájení z obou zdrojů dále do DC komponent musí být přepínač SW10 v poloze 1-2.

Tabulka 3. Výběr zdroje napájení DC 12V

| Zdroj 12V | J3 |

| Konektory DC karty, dodávané buď z J1 nebo J2 | 1–2 (výchozí) |

| Základní deska (přes J55A) | 2-3 |

VCC_12V se dále používá k napájení VBAT_LIN a jako napájení pro ethernetovou PHY desku Sabre, kterou lze připojit přes konektor J53.

VCC_12V se dále používá k napájení VBAT_LIN a jako napájení pro ethernetovou PHY desku Sabre, kterou lze připojit přes konektor J53.

Poznámka: SW10 musí být vždy v poloze 1-2, aby se umožnilo šíření 12V do rozhraní DC karty, a to i v případě, že 12V je dodáváno ze základní desky (J3 zkratován v poloze 2-3).

Tabulka 4. Hlavní napájecí konektorview

| Konektor | Odkaz | Popis |

|

DC: J1 | Tento konektor by měl být použit k připojení dodaného síťového adaptéru. Poznámka: Pokud používáte náhradní nebo alternativní adaptér, musíte se ujistit, že 2.1mm zástrčka používá správnou polarizaci. |

|

DC: J2 | Toto lze použít k připojení holého vodiče k EVB, obvykle z laboratorního zdroje napájení. Polarizace konektorů je na EVB jasně vyznačena. Musíte zajistit správné připojení. |

4.2 Napájecí zdroj EVB VCC_5V0, VCC_3V3

Existují tři možnosti, jak tyto napájecí zdroje připojit k dceřiné kartě. Podrobnosti viz následující tabulky.

Tabulka 5. Konfigurace napájení DC VCC_5V0

| Zdroj VCC_5V0 | J4 | Poznámka |

| Externí napájecí šroubovací konektor (JP1 pin 4) | 1–2 (výchozí) | Obvykle z laboratorního zdroje. Musíte zajistit správné připojení a ujistit se, že je připojeno i uzemnění (GND) (JP1 pin 1 nebo 5). |

| MB až J56A | 2-3 | Ujistěte se, že je J7 na MB sepnutý (1-2 krátce) |

| PMIC | 2-4 | – |

Tabulka 6. Konfigurace napájení DC VCC_3V3

| Zdroj VCC_3V3 | J7 | Poznámka |

| Externí napájecí šroubovací konektor (JP1 pin 3) | 1–2 (výchozí) | Obvykle z laboratorního zdroje. Musíte zajistit správné připojení a ujistit se, že je připojeno i uzemnění (GND) (JP1 pin 1 nebo 5). |

| MB až J56A | 2-3 | Ujistěte se, že je J9 na MB sepnutý (1-2 krátce). |

| PMIC | 2-4 | – |

4.3 Napájecí zdroj EVB 1.5

4.3 Napájecí zdroj EVB 1.5

Existují čtyři možnosti, jak získat 1.5V napájení na dceřiné kartě.

Tabulka 7. Konfigurace napájení DC 1.5 V

| zdroj 1.5V | J6 | J26 | J28 | J29 | Poznámka |

| Externí napájecí šroubovací konektor (JP1 pin 2), obvykle z laboratorního zdroje. | 1–2 (výchozí) | Otevřít (výchozí) | 1–2 (výchozí) | 2–3 (výchozí) | Musíte zajistit správné připojení a ujistit se, že je připojen i GND (JP1 pin 1 nebo 5). Upozorňujeme, že pro tuto možnost musí být J26 ponechán otevřený a J28 musí být nakonfigurován na 1-2 krátké spojení. |

| Buck měnič na MB přes J56A | 2-3 | Ujistěte se, že je J68 na MB sepnutý (1-2 krátké) | |||

| PMIC | 2-4 | ||||

| Interní SMPS | OTEVŘENO | 1-2 | 2-3 | 1-2 (VDD_HV_ A)/2-3 (VDD_HV_ B) | J29 vybírá zdrojový objemtage pro SMPS |

4.4 Nastavení napájení jádra 1.1 V

Ujistěte se, že je J27 sepnutý po dobu 2-3 sekund (výchozí nastavení) pro všechny provozní podmínky. Tím se signál NMOS_CTRL připojí k hradlu externího NFETu, který reguluje 1.1 V napájení jádra a logiky z 1.5 V.

4.5 VDD_HV_A a VDD_HV_B

Domény VDD_HV_A a VDD_HV_B mohou být napájeny buď z VCC_5V0, nebo z VCC_3V3. Výchozí a preferovaná konfigurace je napájet VDD_HV_A z VCC_5V0 a VDD_HV_B z VCC_3V3.

Konfiguraci VDD_HV_A zajišťuje připájený blok R6, který je standardně zkratován na pozice 1-3 (VCC_5V0).

Konfiguraci VDD_HV_B zajišťuje připájený blob R334, který je standardně zkratován na pozici 1-2 (VCC_3V3).

V následující tabulce naleznete možné konfigurace domén napájecích zdrojů VDD_HV_A a VDD_HV_B a omezení periferních zařízení.

Tabulka 8. Konfigurace VDD_HV_A a VDD_HV_B

| VDD_HV_A | VDD_HV_B | SDADC, ADCBIST, MSC, řízení motoru (VDD_HV_A) | Ethernet, QSPI, Zipwire (VDD_HV_B) | ||

| svtage | R6 | svtage | R334 | ||

| VCC_5V0 | 1–3 (výchozí) | VCC_3V3 | 1–2 (výchozí) | K dispozici | K dispozici |

| VCC_5V0 | 1-3 | VCC_5V0 | 1-3 | K dispozici | Není k dispozici |

| VCC_3V3 | 1-2 | VCC_3V3 | 1-2 | Není k dispozici | K dispozici |

4.6 VDD_DCDC

Doménu VDD_DCDC lze napájet buď z VDD_HV_A nebo VDD_HV_B. Výběr napájení VDD_DCDC je možný konfigurací J29.

Upozorňujeme, že J29 nesmí zůstat otevřený, jeden z napájecích zdrojů musí být neustále vybrán.

Tabulka 9. Konfigurace napájení VDD_DCDC

Tabulka 9. Konfigurace napájení VDD_DCDC

| Zdroj VDD_DCDC | J29 |

| VDD_HV_A | 1-2 |

| VDD_HV_B | 2–3 (výchozí) |

4.7 VDD_LVDS

Doménu VDD_LVDS lze napájet pouze ze zdroje 3.3 V. Lze ji připojit buď k VDD_HV_B, nebo k VCC_3V3. J30 nabízí možnosti výběru zdroje napájení. Pokud se nepoužívá Zipwire, může být napájecí doména VDD_LVDS ponechána nepřipojená.

Tabulka 10. Konfigurace napájení VDD_LVDS

| Napájení VDD_LVDS | J30 | Poznámka |

| VCC_3V3 | 1-2 | – |

| VDD_HV_B | 2–3 (výchozí) | Lze nakonfigurovat do této polohy pouze v případě, že je VDD_HV_B napájeno napětím 3.3 V. |

| Bezmotorový | OTEVŘENO | Nenapájený VDD_LVDS nezpůsobuje reset MCU (v tomto případě nelze použít Zipwire a VDD_LVDS je signalizováno příznakem v registru PMC.LVSC). |

4.8 VREFH

Všechny svtagReference MCU jsou připojeny k jedinému zdroji VREFH, který se doporučuje zkratovat s VDD_HV_A na úrovni plošného spoje, nebo jej lze napájet z PMIC. Všechny piny VREFH_x musí být napájeny za všech podmínek a nesmí zůstat nezapojené. Konfigurace se povoluje pomocí J63.

Tabulka 11. Konfigurace zdroje VREFH

| Zdroj VREFH | J63 |

| PMIC VREF | 1-2 |

| VDD_HV_A | 2–3 (výchozí) |

5.1 Reset, probuzení a LED indikátor

Na DC kartě se nachází přepínač RESET (SW3), který umožňuje ruční generování resetovacího signálu pro mikrokontrolér S32K396, který resetuje periferie osazené na DC kartě signálem RESET. LED dioda RESET (D15) svítí (červeně), když je signál RESET aktivní (konektor J31 je sepnutý).

Signál RESET_b je obousměrný a je směrován do několika rozhraní na DC kartě a do MB přes konektory rozhraní MB_DC (viz následující tabulka).

Tabulka 12. Směrování signálu RESET_b

| RESET_b připojení | DC reference | Popis |

| ETM Mictor Trace | J22 | Po sepnutí je RESET_b směrován na konektor ETM Mictor Trace. |

| Rameno J.TAG ladit | J23 | Po sepnutí je RESET_b směrován do ramene J.TAG ladicí konektor. |

| FS26 | J12 | Po sepnutí je RESET_b směrován na FS26. |

| Resetovací tlačítko | J31 | Po sepnutí je RESET_b směrován na SW3. |

| QSPI | J36 | Po zavření je RESET_b směrován do externí paměti QSPI. |

| Ethernet | J60 | Po sepnutí je RESET_b směrován na externí konektor Sabre a také na ethernetový PHY na základní desce. |

| USB/sériový | J67 | V sepnutém stavu je RESET_b směrován z GPIO řízeného rozhraním USB/sériové rozhraní do MCU. |

Pro účely externího zdroje probuzení je SW4 směrován na PTB19, který implementuje funkci probuzení vstupem WKPU[38]. Toto je jeden ze způsobů, jak probudit MCU z pohotovostního režimu.

5.2 Rozhraní ladění

Na DC kartě existují tři možné možnosti pro ladění sdílení stejných signálů. Směrování signálů pro jednotlivá ladicí rozhraní lze vybrat pomocí propojek J16, J17, J18 a J19. Viz popis konfigurace u těchto tří možností.

Tabulka 13. Výběr ladicího rozhraní

| Debug rozhraní | J16, J17, J18, J19 |

| Rameno J.TAG | 2–4 (výchozí) |

| Mictor Trace | 2-3 |

| OpenSDA | 1-2 |

Tabulka 14. Rozhraní ladění DC karty přesview

| Konektor | DC reference | Popis | |

| 20kolíkové rameno standardní JTAG konektor |

|

J20 | Podporuje to J.TAG rozhraní pro přístup k zařízením založeným na ARM7 a ARM9. Pro zařízení Cortex-MX podporuje Serial Wire a JTAG rozhraní pro přístup ke všem SWD, SWV a JTAG signály dostupné na zařízení Cortex-Mx. |

| 38pinový konektor Arm ETM Mictor |

|

P1 | Mictor (Matched Impedance Connector) byl standardním způsobem připojení trasovací sondy k cílovému zařízení Arm. Cortex-M7 podporuje 16bitové trasování dat pomocí konektoru Mictor. Toto je k dispozici pouze u DS-5 s použitím ladicí a trasovací jednotky DSTREAM. |

| OpenSDA |

|

J15 | Konektor micro USB se používá k připojení k integrovanému ladicímu rozhraní OpenSDA, které přemosťuje sériovou a ladicí komunikaci mezi hostitelem USB a integrovaným cílovým procesorem. Ladicí obvod je založen na mikrokontroléru Kinetis MK65. |

USB rozhraní

Na DC kartě je LPUART0 směrován do ladicího rozhraní OpenSDA (J15), které také podporuje přenos komunikace z USB do sériového rozhraní.

K dispozici je také rozhraní MCP2221 (U32) pro převod USB na UART/I2C s funkcí GPIO. Používá konektor J64 typu USB-B a je připojeno k instancím LPI2C0 a LPUART2.

Tabulka 15. Rozhraní USB-sériové na stejnosměrném napájení

| Rozhraní | Stejnosměrný referenční proud | Název signálu | port MCU |

Popis |

|

| OpenSDA

|

J15 | LPUART0_RX | 10 XNUMX PTE | Příjem UART | |

| LPUART0_TX | 11 XNUMX PTE | Přenos UART | |||

| USB/sériový port

|

J64

|

LPUART2_RX | PTH9 | Příjem UART | |

| LPUART2_TX | PTH8 | Přenos UART | |||

| LPI2C0_SDA | PTF21 | Datové vstupy/výstupy LPI2C | |||

| LPI2C0_SCL | PTF20 | Vstup/výstup hodin LPI2C | |||

| USB_RESET | RESET_B | Když je J67 obsazen, může ovládat signál resetu. | |||

LIN rozhraní

Na obvodu S32K396 DC je osazen duální LIN transceiver TJA1022, který je schopen pracovat v režimu Master i Slave (volitelné propojkami: J50 a J51) a jeho výstupy jsou připojeny ke konektoru rozhraní LIN J52. Mikrokontrolér komunikuje s ovladačem přes LPUART.

Tabulka 16. Konfigurace LIN PHY

Tabulka 16. Konfigurace LIN PHY

| LIN PHY | Pozice skokana | Konfigurace |

| 1 (J50) | Otevřít (výchozí) | Otrok |

| blízko | Zvládnout | |

| 2 (J51) | Otevřít (výchozí) | Otrok |

| Blízko | Zvládnout |

Zapojení pinů LIN konektoru je podrobně popsáno v následující tabulce.

Tabulka 17. Konektor rozhraní LIN J52

| Číslo PIN | Signál |

| 1 | GND |

| 2 | GND |

| 3 | NC |

| 4 | NC |

| 5 | VBAT_LIN |

| 6 | VBAT_LIN |

| 7 | LIN2 |

| 8 | LIN1 |

Seznam signálů připojených z MCU k transceiveru LIN je uveden v následující tabulce. Signály MCU pro LIN1 pocházejí z napájecí domény VDD_HV_A a signály pro LIN2 pocházejí z domény VDD_HV_B.

Tabulka 18. LIN připojení z MCU k LIN transceiveru na desce stejnosměrného proudu

| LIN rozhraní | Název signálu MCU | port MCU |

| 1 | LPUART3_RX | PTC20 |

| LPUART3_TX | 1 XNUMX PTE |

| LIN rozhraní | Název signálu MCU | port MCU |

| 2 | LPUART2_RX | PTC12 |

| LPUART2_TX | PTC13 |

Rozhraní CAN

8.1 Rozhraní CAN na dceřiné kartě (DC)

Na kartě S32K396 DC1 je osazen jeden CAN transceiver TJA1044GT. Signály CAN jsou směrovány na konektor J34 a pocházejí z napájecí domény VDD_5V0. Pohotovostní režim pro PHY lze ovládat pomocí J35 (Pohotovostní režim: 1-2; Normální (výchozí): 2-3).

Tabulka 19. Připojení CAN z MCU k vysílači/přijímači CAN na desce stejnosměrného proudu

Tabulka 19. Připojení CAN z MCU k vysílači/přijímači CAN na desce stejnosměrného proudu

| Název signálu | port MCU | Popis | Poznámka | |

| CAN0_TX | PTC21 | CAN Tx kanál | ||

| CAN0_RX | PTC23 | Kanál CAN Rx |

Ethernet rozhraní

Na kartě S32K396 EVB není žádný ethernetový PHY, ale ethernetové rozhraní poskytující signály MII a/nebo RMII je směrováno do konektoru Sabre J53. Lze tam zapojit a používat rozšiřující desku Sabre pro ethernetový PHY.

Tabulka 20. Konfigurace ethernetových signálů pro rozhraní PHY na DC a MB

| Signál | Konfigurační rezistory na DC | Povolení rozhraní DC SABRE: konfigurace rezistoru | MB TJA1103A PHY enable: konfigurace rezistoru |

| EMAC_MII_RMII_MDC | R521 | DNP | Zalidněno |

| EMAC_MII_RMII_MDIO | R530 | DNP | Zalidněno |

| EMAC_MII_RMII_TX_EN | R532 | DNP | Zalidněno |

| EMAC_MII_RMII_RX_ER | R522 | DNP | Zalidněno |

| EMAC_MII_CRS | J61 | OTEVŘENO | J61 krátký 2-3 |

| EMAC_MII_RXD3 | R529 | DNP | Zalidněno |

| EMAC_MII_RMII_RXD[0] | R519 | DNP | Zalidněno |

| EMAC_MII_RMII_RXD[1] | R528 | DNP | Zalidněno |

| EMAC_MII_RXD2 | R520 | DNP | Zalidněno |

| EMAC_MII_TXD3 | R534 | DNP | Zalidněno |

| EMAC_MII_TXD2 | R538 | DNP | Zalidněno |

| EMAC_MII_RMII_TXD[1] | R533 | DNP | Zalidněno |

| EMAC_MII_RMII_TXD[0] | R537 | DNP | Zalidněno |

| EMAC_MII_RMII_TX_CLK | R536 | DNP | Zalidněno |

| EMAC_MII_RX_CLK | R539 | DNP | Zalidněno |

| EMAC_MII_RMII_RX_DV | J61 | OTEVŘENO | J61 krátký 1-2 |

Následující obrázek znázorňuje rozhraní SABRE J53 pro připojení vývojové desky SABRE TJA1103SDB.

Ujistěte se, že rezistory R266, R519, R520, R521, R522, R528, R529, R530, R532, R533, R534, R536, R537, R538, R539 jsou DNP a J61 je otevřený pro použití vývojové desky SABRE TJA1103SDB.

Tabulka 21. Signály Ethernetu směrované do konektoru rozhraní Sabre v režimu DC

| Signál | port MCU | Popis |

| EMAC_MII_RMII_MDC | PTD17 | ENET hodiny pro přenos řídicích dat do PHY |

| EMAC_MII_RMII_MDIO | PTD16 | Řídicí data ENET do/z PHY |

| EMAC_MII_RMII_TX_EN | 9 XNUMX PTE | Povolení přenosu ENET |

| EMAC_MII_RMII_RX_ER | PTC16 | Chyba příjmu ENET |

| EMAC_MII_COL | PTB27 | Detekována kolize ENET MII |

| EMAC_MII_RXD3 | PTC15 | Příjem dat ENET (pouze režim MII) |

| EMAC_MII_RMII_RXD[0] | PTB23 | ENET přijímá data |

| EMAC_MII_RMII_RXD[1] | PTB24 | ENET přijímá data |

| EMAC_MII_RXD2 | PTC14 | Příjem dat ENET (pouze režim MII) |

| EMAC_MII_TXD3 | PTB3 | Přenos dat ENET (pouze režim MII) |

| EMAC_MII_TXD2 | PTB28 | Přenos dat ENET (pouze režim MII) |

| EMAC_MII_RMII_TXD[1] | PTB29 | ENET přenáší data |

| EMAC_MII_RMII_TXD[0] | PTC18 | ENET přenáší data |

| EMAC_MII_RMII_TX_CLK | PTC19 | Vysílací hodiny ENET |

| EMAC_MII_RX_CLK | PTB26 | Přijímací hodiny ENET MII |

| EMAC_PPS1 | PTD13 | Časový kanál ENET 1588 |

| EMAC_PPS0 | PTA26 | Časový kanál ENET 1588 |

| EMAC_MII_CRS | PTB22 | Snímání nosné ENET MII |

| EMAC_MII_RMII_RX_DV | PTD14 | Platná přijatá data ENET |

Poznámka Tyto signály jsou vyhrazeny pro ethernetové rozhraní a směrovány do konektoru Sabre.

Rozhraní QSPI

Na desce stejnosměrného proudu je osazena paměť S71KL512SC0 3.0V 512 Mb HyperFlash a 64 Mb HyperRAM v multičipovém pouzdře. Výběr cílové paměti se provádí pomocí odpovídajícího signálu pro výběr čipu. Paměť je připojena k rozhraní QSPI mikrokontroléru S32K396, který má pouze jeden výběr čipu, takže výběr se provádí pájeným rezistorem R328 (standardně 1-2, výběr Hyper Flash).

Tabulka 22. Konfigurace výběru paměťového čipu QSPI

| Vybraná paměť | R328 | Popis |

| Hyper Flash | 1–2 (výchozí) | QSPI_PCSFA je připojen k pinu CS1 externí paměti |

| Hyper-RAM | 2-3 | QSPI_PCSFA je připojen k pinu CS2 externí paměti |

Pro signál RESET_b se používá pouze přepínač úrovní, protože tento pin je napájen z domény VDD_HV_A. Signál resetování lze odpojit od paměti QSPI pomocí konektoru J36 (výchozí nastavení je zavřené).

Varování

Rozhraní QSPI je napájeno z domény VDD_HV_B, takže paměť QSPI lze použít pouze tehdy, když je VDD_HV_B napájeno z VCC_3.0V (výchozí konfigurace). V případě, že je VDD_HV_B překonfigurováno na napájení z VCC_5.0V, je nutné odstranit rezistory s nulovým odporem (viz tabulka níže), které spojují signály QSPI z MCU s pamětí.

Tabulka 23. Signál QSPI přesview

| port MCU | Název signálu | Sériový rezistor | Popis |

| PTD11 | QuadSPI_IOFA0 | R316 | Sériová data QuadSPI pro sériové flash zařízení A (rychlé) |

| PTD7 | QuadSPI_IOFA1 | R322 | Sériová data QuadSPI pro sériové flash zařízení A (rychlé) |

| PTD12 | QuadSPI_IOFA2 | R317 | Sériová data QuadSPI pro sériové flash zařízení A (rychlé) |

| PTC2 | QuadSPI_IOFA3 | R318 | Sériová data QuadSPI pro sériové flash zařízení A (rychlé) |

| PTC0 | QuadSPI_IOFA4 | R319 | Sériová data QuadSPI pro sériové flash zařízení A (rychlé) |

| PTD9 | QuadSPI_IOFA5 | R324 | Sériová data QuadSPI pro sériové flash zařízení A (rychlé) |

| PTD8 | QuadSPI_IOFA6 | R320 | Sériová data QuadSPI pro sériové flash zařízení A (rychlé) |

| PTC17 | QuadSPI_IOFA7 | R321 | Sériová data QuadSPI pro sériové flash zařízení A (rychlé) |

| PTD10 | QuadSPI_SCKFA | R326 | Sériové hodiny QuadSPI pro sériové flash zařízení A (rychlé) |

| PTC1 | QuadSPI_DQSFA | R325 | Signál stroboskopu dat QuadSPI Flash A (RWDS) |

| PTC3 | QuadSPI_PCSFA | R327 | Výběr čipu QuadSPI pro sériové flash zařízení A |

Zipline

Na desce stejnosměrného proudu je osazen konektor rozhraní Zipwire. Typ konektoru je Samtec (ERF8-005-05.0-L-DV-L-TR). Na signálech Zipwire jsou také osazeny praktické testovací body, které jsou užitečné pro ladění a vyhodnocování výkonu.

Následující tabulka popisuje konektor.

Následující tabulka popisuje konektor.

Tabulka 24. Popis konektoru rozhraní Zipwire

| Konektor | Tag | Číslo PIN | Signál |

|

J41 | 1 | TX_P |

| 2 | GND | ||

| 3 | TX_N | ||

| 4 | GND | ||

| 5 | GND | ||

| 6 | REF_CLK | ||

| 7 | RX_N | ||

| 8 | GND | ||

| 9 | RX_P | ||

| 10 | GND | ||

| 11 | GND | ||

| 12 | GND |

Připojení signálu k rozhraní Zipwire z MCU je uvedeno v následující tabulce.

Tabulka 25. Připojení rozhraní Zipwire k mikrokontroléru

| Rozhraní Zipwire | Název signálu | MCU port/pin | Popis |

| RX_N | LFAST_0_RxD_N | – | LVDS přijímá záporný pól |

| RX_P | LFAST_0_RxD_P | – | LVDS přijímá kladný pól |

| TX_N | LFAST_0_TxD_N | – | Záporný pól přenosu LVDS |

| TX_P | LFAST_0_TxD_P | – | LVDS přenáší kladný pól |

| REF_CLK | LFAST_0_EXT_REF_I/O | PTA29 | Vstup/výstup referenčních hodin LFAST |

Testovací body, kde lze přistupovat k signálům LFAST, jsou uvedeny v následující tabulce.

Tabulka 26. Testovací body pro signály LFAST

| Test bod | Název signálu |

| TP45 | LFAST_0_RxD_N |

| TP48 | LFAST_0_RxD_P |

| TP47 | LFAST_0_TxD_N |

| TP44 | LFAST_0_TxD_P |

| TP46 | LFAST_0_EXT_REF_I/O |

Mikrosekundový kanál

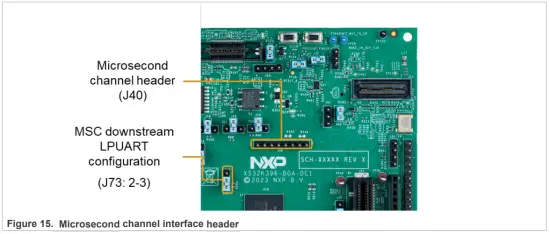

Komunikační rozhraní mikrosekundového kanálu (MSC) se skládá ze dvou IP adres. Pro upstream kanál používá rozhraní DSPI se signály LVDS (datové a hodinové signály) a pro downstream kanál rozhraní UART (pouze UART Rx kanál). Signály výběru čipu a UART RX jsou signály s jedním koncem. Mikrosekundové kanály jsou k dispozici na konektoru J40. Pro použití mikrosekundového kanálu je nutné nasadit J73 na pozici 2-3. -3 (výchozí 1-2 pro napájení SBC).

Tabulka 27. Signál rozhraní mikrosekundového kanálu přesview

| Signál | Port/plocha MCU | Popis | Poznámka |

| DSPI_MSC0_SCK_N | -/U16 | Záporný terminál výstupních hodin LVDS MSC | Vyhrazené LVDS kontakty, nemultiplexované s žádnou jinou funkcí. Lze použít pouze tehdy, když je VDD_HV_A napájeno z VCC_5V0, protože tyto piny jsou napájeny z VDD_HV_A. |

| DSPI_MSC0_SCK_P | -/U15 | Kladný terminál výstupních hodin LVDS MSC | |

| DSPI_MSC0_SOUT_N | -/T14 | Záporný terminál datového výstupu LVDS MSC | |

| DSPI_MSC0_SOUT_P | -/U13 | Kladný pól datového výstupu LVDS MSC | |

| DSPI_MSC0_PCS[0] | PTF14/F15 | Výběr periferního čipu DSPI MSC 0 | – |

| DSPI_MSC0_PCS[1] | PTF15/F14 | Výběr periferního čipu DSPI MSC 1 | – |

| LPUART_MSC0_RX | PTF26/R12 | Následný UART Rx kanál | – |

Tabulka 28. Konfigurace J73

| Funkce PTF26 | J73 |

| Komunikace LPSPI s FS26 | 1–2 (výchozí) |

| Následný kanál MSC LPUART | 2-3 |

Rozhraní pro řízení motoru

Na DC měniči je jeden konektor rozhraní pro řízení motoru (podrobný popis a přiřazení signálu viz Tabulka 31). Rozhraní pro řízení motoru je k dispozici pouze tehdy, když VDD_HV_A používá VDD_5V0. Toto rozhraní je kompatibilní s nízkonapěťovýmitage (GD33937) a vysoce objemovýtagDesky budičů hradel e (GD3162). Následující tabulka popisuje funkci každého pinu. Protože vysoké napětítagDeska budiče hradla má trochu odlišnou funkčnost, rozdíly jsou v tabulce uvedeny tučně.

Pozor

Je nutné zvolit budicí signál pro resolver pomocí J45.

Tabulka 29. Připojení rozhraní pro řízení motoru na stejnosměrném proudu

| Rozhraní pro řízení motoru | ||||||||

| Směrování MCU/desky | Funkce | Jméno | Kolík | Jméno | Funkce | Směrování MCU/desky | ||

| VCC_5V0 | Analogový zdroj referenčního napětí | VREF | B1 | A1 | VDDA | Analogové napájení | VDD_5V0 | |

| AGND | Analogové uzemnění | GNDA2 | B2 | A2 | GNDA1 | Analogové uzemnění | AGND | |

| 18 XNUMX PTE | Proud stejnosměrné sběrnice | A0 | B3 | A3 | A1 | Proud U fáze | PTD1 | |

| PTA8 | DC sběrnice objtage | A2 | B4 | A4 | A3 | Fázový proud V | 26 XNUMX PTE | |

| NC | Analogový vstup | A4 | B5 | A5 | A5 | Fázový proud W | PTA24 | |

| NC | Analogový vstup | A6 | B6 | A6 | A7 | Analogový vstup | NC | |

| NC | Analogový vstup | A8 | B7 | A7 | A9 | Analogový vstup | NC | |

| 6 XNUMX PTE | Rezolver sinusový negativní diferenciál | A10 | B8 | A8 | A11 | Resolver sinusový jednoduchý/diferenciální kladný | 2 XNUMX PTE | |

| 17 XNUMX PTE | Rezolver cos negativní diferenciál | A12 | B9 | A9 | A13 | Rezolver cos jednoduchý/diferenciální kladný | PTA16 | |

| NC | – | 14 | B10 | A10 | A15 | Analogový vstup/ EXC_SIG_DEN | NC | |

| AGND | Analogové uzemnění | GNDA3 | B11 | A11 | GNDA4 | Analogové uzemnění | AGND | |

| VDD_HV_A | Digitální napájecí zdroj MC | U_VCC | B12 | A12 | VCC_PER | Digitální napájecí zdroj | VDD_HV_A | |

| GND | Digitální zem | GND1 | B13 | A13 | GND2 | Digitální zem | GND | |

| PTF0 | U_Tranzistor_Teplota_V/Enkodér_A | TM0 | B14 | A14 | PWM0 | PWM fáze UH | PTD24 | |

| PTF9 | U_Tranzistor_Teplota_L/Encoder_B | TM1 | B15 | A15 | PWM1 | PWM fáze UL | PTA2 | |

| PTF4 | V_Teplota_tranzistoru_L/Index_kodéru | TM2 | B16 | A16 | PWM2 | PWM fáze VH | PTA3 | |

| PTF5 | V_Tranzistor_Teplota_H | TM3 | B17 | A17 | PWM3 | PWM fáze VL | PTD23 | |

| 27 XNUMX PTE | Teplota_tranzistoru_W | TM4 | B18 | A18 | PWM4 | PWM fáze WH | PTD2 | |

| PTB12/SWG0 | Buzení resolveru | TM5 | B19 | A19 | PWM5 | PWM fáze WL | PTD3 | |

| PTF14 | Tlačítko Spustit | IO1 | B20 | A20 | PWM6 | Výpust U_GS | 19 XNUMX PTE | |

| PTA20 | SPI_MISO | MISO | B21 | A21 | PWM7 | U_GS Nabíjení/Brzdění PWM | PTB2 | |

| PTA18 | SPI_MOSI | LELKOVAT | B22 | A22 | PWM8 | Fáze vybíjení/nulového průchodu V_GS U | PTA30 | |

| PTA19 | SPI_SCK | SCKL | B23 | A23 | PWM9 | V_GS Nabíjení/nulový průchod Fáze V | PTB18 | |

| PTA21 | SPI CS Nízký/SPI CS | /SS | B24 | A24 | PWM10 | W_GS Vybíjení/ průnik nulou Fáze W | PTB21 | |

| PTA17 | Teplota tranzistoru W | IO2 | B25 | A25 | PWM11 | Poplatek za W_GS | PTA31 | |

| PTG3 | Kontrola zapnutí tranzistoru W/UART TXD | SCI_TXD | B26 | A26 | CHYBA 1 | INTB_HS/Porucha_OC | PTB15 | |

| PTG8 | Kontrola zapnutí tranzistoru L/UART RXD | SCI_RXD | B27 | A27 | CHYBA 2 | INTB_LS/Porucha_OV | PTB16 | |

| PTA14 | Povolení bezpečnostního režimu/povolení GD | IO3 | B28 | A28 | CHYBA 3 | Kontrola zapnutí tranzistoru U | PTD20 | |

| PTA23 | Reset poruchy nízkého napájecího napětí/GD | IO4 | B29 | A29 | CHYBA 4 | Kontrola zapnutí/vypnutí tranzistoru U | PTB17 | |

| PTG4 | Stav poruchy na straně vysokého napětí/GD INT | IO5 | B30 | A30 | IO6 | SPI CS Vysoký | PTA22 | |

| VCC_12V | Napájení 12V | VPOWER | B31 | A31 | IO7 | Kontrola zapnutí tranzistoru V/Přepínač | PTB5 | |

| GND | Digitální GND/ Napájecí GND | GNDP | B32 | A32 | IO8 | Kontrola zapnutí/vypnutí tranzistoru L/SW | PTB13 | |

Tabulka 30. Výběr budicího signálu resolveru

| Zdroj budicího signálu resolveru | J45 |

| Generátor sinusových vln 0 | 1-2 |

| eTPU_B_CH[2]/eTPU_A_[0]/pin GPIO | 2-3 |

Uživatelské rozhraní

K dispozici je několik pinových konektorů, kde je k dispozici více signálů, a také tři uživatelské LED diody a čtyři tlačítka.

Tabulka 31. Souhrn uživatelského rozhraní

| Modul | DC reference | Popis |

| I2C | J39 | Rozhraní LPI2C1 |

| FlexIO | J62 | 32 signálů FlexIO dostupných na konektoru |

| eMIOS0 | J58 | 8 signálů eMIOS dostupných na headerech |

| Uživatelská LED | D35 | Port mikrokontroléru PTH7 konfigurovaný jako GPIO |

| D34 | Port MCU PTD4 konfigurovaný jako GPIO | |

| D33 | Port MCU PTD5 konfigurovaný jako GPIO | |

| Uživatelská tlačítka | SW5 | Port mikrokontroléru PTE21 konfigurovaný jako GPIO. Pro výběr funkce SW71 je nutné zkratovat J2 na pozice 3-5. |

| SW7 | Port MCU PTG2 konfigurovaný jako GPIO | |

| SW8 | Port MCU PTG1 konfigurovaný jako GPIO | |

| SW9 | Port MCU PTG0 konfigurovaný jako GPIO |

Rozhraní pro správu baterií

Pro komunikaci se subsystémem baterií jsou k dispozici osazené izolované síťové vysokorychlostní transceivery MC33664ATL1EG. MCU komunikuje se zařízením prostřednictvím dvou rozhraní LPSPI (LPSPI2 – master, LPSPI3 – slave) a dvou pinů GPIO. Rozhraní pro správu baterií (BMS) využívá konektor J59.

Tabulka 32. Signál rozhraní BMS přesview

| Modul | Funkčnost | port MCU | Popis |

| LPSPI2 | SCK | PTF0 | Komunikace proti proudu |

| PCS0 | PTF3 | ||

| JIŽ | PTF2 | ||

| GPIO | EN | PTH11 | Ovládání režimu zařízení BMS (Normální/Spánek) |

| LPSI3 | SCK | PTF13 | Komunikace po proudu |

| PCS0 | PTF16 | ||

| HŘÍCH | PTF12 | ||

| GPIO | INT | PTH12 | Přerušení BMS pro spuštění probuzení zařízení |

Monitorování interního signálu

Modul TRGMUX_APP umožňuje monitorovat interní spouštěče přes piny. Na EVB je k dispozici 9 z 16 výstupů TRGMUX, jak je znázorněno v následující tabulce.

Pro směrování interních signálů na piny je třeba nakonfigurovat následující:

- Výstupní funkce pinu jako výstup TRGMUX v modulu SIUL2 (SIUL2.MSCR[x].B.SSS)

- Výstupní buffer povolen v modulu SIUL2 (SIUL2.MSCR[x].B.OBE)

- Vybraný signál je třeba nakonfigurovat v modulu TRGMUX_AP na základě výběru provedeného na základě tabulky S32K39_and_S32K37_TRMUX_connectivity.xlsx/S32K36_TRMUX_connectivity.xlsx připojené k RM. Signály eTPU lze také směrovat přes TRGMUX_APP na pinech, ale k tomu je nutné je směrovat do TRGMUX_APP (signály TRGMUX_MSC_TRGMUX_IN0 – TRGMUX_MSC_TRGMUX_IN9) konfigurací TRGMUX_MSC (registry TRGMUX_APP_TRGMUX_OUT0 – TRGMUX_APP_TRGMUX_OUT9).

- Počet vstupních signálů TRGMUX_APP je omezen na 128 a pro jejich rozšíření se používá funkcionalita monitorovacího multiplexeru, která směruje další interní signály do TRGMUX_APP na vstupy 2, 3 a 4 konfigurací registrů monitorovacího multiplexeru umístěných v modulu SIUL2 (MUX0_TIMER_EN1, MUX0_BCTU1_EN, MUX1_TIMER_EN0, MUX1_BCTU0_EN, MUX1_MISC_EN, MUX2_TIMER_EN1, MUX2_BCTU1_EN, MUX2_MISC_EN). Tyto signály jsou uvedeny v listu Monitorovacího multiplexeru ve výše uvedené tabulce. Pokud chcete mít na vstupu TRGMUX_APP jeden interní signál, stačí nastavit pouze jeden bit v daném registru MUX, protože tyto signály jsou před vstupem na vstup TRGMUX_APP seřazeny pomocí operace OR.

Tabulka 33. Souhrn výstupních signálů TRGMUX_OP

| TRGMUX_OUTPUT | Portový kolík | Směrování desky | MSCR | MSCR[SSS] | TRGMUX_ Registrace aplikace | TRGMUX_APP číslo bitového pole registru SEL |

| 0 | 5 XNUMX PTE | J62.8 | 133 | 0x8 | SIUL_ OUT_0 (32) | 0 |

| 1 | PTD0 | TP95 | 96 | 0x7 | 1 | |

| 4 | 10 XNUMX PTE | TP90 | 138 | 0x7 | SIUL_ OUT_1 (33) | 0 |

| 5 | 11 XNUMX PTE | TP88 | 139 | 0x7 | 1 | |

| 8 | PTA31 | J44.A25 | 31 | 0x7 | SIUL_ OUT_2 (34) | 0 |

| 9 | PTB18 | J44.A23 | 50 | 0x7 | 1 | |

| 10 | PTB19 | J32.2 | 51 | 0x7 | 2 | |

| 12 | PTB21 | J44.A24 | 53 | 0x7 | SIUL_ OUT_3 (35) | 0 |

| 13 | PTB22 | J61.3 | 54 | 0x7 | 1 |

Výchozí konfigurace propojky

Tabulka 34. Výchozí konfigurace propojek

| Modul | Funkčnost | DCreference | Výchozí připojení | Popis |

| Rozložení vstupního výkonu | VCC_12V | J3 | 1-2 | Hlavní napájení je přiváděno z konektorů DC karty, které jsou přivedeny buď na J1, nebo J2. |

| VCC_5V0 | J4 | 1-2 | Napájeno z externího šroubovacího konektoru (JP1 pin 4). | |

| VCC_1V5 | J6 | 1-2 | Napájeno z externího šroubovacího konektoru (JP1 pin 2). | |

| VCC_3V3 | J7 | 1-2 | Napájeno z externího šroubovacího konektoru (JP1 pin 3). | |

| VDD_HV_B | R334 | 1-2 | Napájeno z VCC_3V3. | |

| VDD_HV_A | R6 | 1-3 | Napájeno z VCC_5V0. | |

| FS26 PMI

|

Režim ladění | J10 | ZAVŘENO | Ladicí pin je připojen k kladnému napětítage pro povolení režimu ladění. |

| J11 | OTEVŘENO | Při konfiguraci FS26 pro režim ladění zůstává otevřené. | ||

| Reset/Probuzení | J12 | ZAVŘENO | Signál RESET_b je připojen k pinu WAKE2 a RSTB mikrokontroléru FS26. | |

| SPI rozhraní | J71 | 1-2 | PTE21 směrován do FS26 jako SIN | |

| J73 | 1-2 | PTF26 směrováno do FS26 jako PCS1 | ||

| J75 | 2-3 | PTC11 směrován do FS26 jako SOUT | ||

| Ladit | Vyberte rozhraní | J16 | 2-4 | Rameno J.TAG konektor vybraný pro signál TDI. |

| J17 | 2-4 | Rameno J.TAG konektor vybraný pro signál TMS. | ||

| J18 | 2-4 | Rameno J.TAG konektor vybraný pro signál TCK. | ||

| J19 | 2-4 | ARM JTAG konektor vybraný pro signál TDO. | ||

| Moc | J21 | ZAVŘENO | VDD_HV_A připojeno k pinu 2 Arm JTAG ladicí konektor. | |

| Resetovat | J22 | ZAVŘENO | Signál RESET_b připojen ke konektoru trasy Arm ETM Mictor. | |

| J23 | ZAVŘENO | Signál RESET_b připojen k Arm JTAG ladicí konektor. | ||

| J68 | OTEVŘENO | Nech tento svetr otevřený | ||

| Napájení mikrokontroléru

|

VDD_1V5 | J26 | OTEVŘENO | Zdroj z externího zdroje, nikoli z interního SMPS mikrokontroléru. |

| Řízení hradla NMOS | J27 | 2-3 | Signál NMOS_CTRL z MCU připojeného k hradlu externího NFETu pro regulaci 1.1V napájení jádra a logiky dolů z 1.5V. | |

| Řízení hradla PMOS | J28 | 1-2 | Hradlo P-MOS tranzistoru je zkratováno s VDD_DCDC. PMOS_CTRL je ponecháno otevřené. | |

| VDD_DCDC | J29 | 2-3 | Zdroj z VDD_HV_B. | |

| VDD_LVDS | J30 | 2-3 | Zdroj z VDD_HV_B. |

Zkratky

MCU – mikrokontrolérová jednotka

EVB – Hodnotící komise

DC – Karta dcery

MB – Základní deska

PMIC – Integrovaný obvod pro správu napájení

ESD – elektrostatický výboj

PHY – Fyzické rozhraní

SMPS – spínaný napájecí zdroj

USB – Univerzální sériová sběrnice

MSC – mikrosekundový kanál

BMS – Battery Management System

Historie revizí

Historie revizí

| ID dokumentu | Datum vydání | Popis |

| UM12212 v.1.0 | 03. února 2025 | Počáteční vydání |

Právní informace

Definice

Koncept — Stav konceptu na dokumentu označuje, že obsah je stále pod interní revizíview a podléhá formálnímu schválení, které může vést k úpravám nebo doplnění. NXP Semiconductors neposkytuje žádná prohlášení ani záruky ohledně přesnosti nebo úplnosti informací obsažených v pracovní verzi dokumentu a nenese žádnou odpovědnost za důsledky použití takových informací.

Vyloučení odpovědnosti

Omezená záruka a odpovědnost – Informace v tomto dokumentu jsou považovány za přesné a spolehlivé. Společnost NXP Semiconductors však neposkytuje žádná prohlášení ani záruky, výslovné ani implicitní, ohledně přesnosti nebo úplnosti těchto informací a nenese žádnou odpovědnost za důsledky použití těchto informací. Společnost NXP Semiconductors nepřebírá žádnou odpovědnost za obsah tohoto dokumentu, pokud je poskytnut informačním zdrojem mimo společnost NXP Semiconductors. Společnost NXP Semiconductors v žádném případě nenese odpovědnost za žádné nepřímé, náhodné, sankční, zvláštní nebo následné škody (včetně – mimo jiné – ušlého zisku, ušlých úspor, přerušení provozu, nákladů souvisejících s odstraněním nebo výměnou jakýchkoli produktů nebo poplatků za přepracování), ať už jsou tyto škody založeny na občanskoprávním deliktu (včetně nedbalosti), záruce, porušení smlouvy nebo jakékoli jiné právní teorii.

Bez ohledu na jakékoli škody, které by mohly zákazníkovi z jakéhokoli důvodu vzniknout, bude souhrnná a kumulativní odpovědnost NXP Semiconductors vůči zákazníkovi za produkty popsané v tomto dokumentu omezena v souladu s podmínkami komerčního prodeje NXP Semiconductors.

Právo na změny – Společnost NXP Semiconductors si vyhrazuje právo kdykoli a bez předchozího upozornění provádět změny informací zveřejněných v tomto dokumentu, včetně specifikací a popisů produktů. Tento dokument nahrazuje veškeré informace poskytnuté před jeho vydáním. Použití – Použití zde popsaná pro kterýkoli z těchto produktů slouží pouze pro ilustrační účely. Společnost NXP Semiconductors neposkytuje žádné prohlášení ani záruku, že takové použití bude vhodné pro specifikované použití bez dalšího testování nebo úprav.

Zákazníci jsou zodpovědní za návrh a provoz svých aplikací a produktů využívajících produkty NXP Semiconductors a NXP Semiconductors nepřijímá žádnou odpovědnost za jakoukoli pomoc s aplikacemi nebo návrhem zákaznických produktů. Je výhradní odpovědností zákazníka určit, zda je produkt NXP Semiconductors vhodný a vhodný pro zákazníkovy aplikace a plánované produkty, jakož i pro plánovanou aplikaci a použití zákazníkem (zákazníků) jako třetí strana. Zákazníci by měli poskytnout vhodné konstrukční a provozní záruky, aby minimalizovali rizika spojená s jejich aplikacemi a produkty.

NXP Semiconductors nepřijímá žádnou odpovědnost související s jakýmkoli selháním, poškozením, náklady nebo problémem, který je založen na jakékoli slabosti nebo selhání v aplikacích nebo produktech zákazníka nebo v aplikaci nebo použití zákazníkem (zákazníky třetí strany) zákazníka. Zákazník je odpovědný za provedení všech nezbytných testů pro aplikace a produkty zákazníka využívající produkty NXP Semiconductors, aby se zabránilo selhání aplikací a produktů nebo aplikace nebo použití zákazníkem (zákazníky třetí strany) zákazníka. NXP nenese v tomto ohledu žádnou odpovědnost.

Podmínky komerčního prodeje — Produkty NXP Semiconductors se prodávají v souladu se všeobecnými podmínkami komerčního prodeje, jak jsou zveřejněny na https://www.nxp.com/profile/terms, není-li v platné písemné individuální dohodě dohodnuto jinak. V případě uzavření individuální smlouvy platí pouze podmínky příslušné smlouvy. Společnost NXP Semiconductors tímto výslovně nesouhlasí s uplatňováním všeobecných obchodních podmínek zákazníka s ohledem na nákup produktů NXP Semiconductors zákazníkem.

Vhodnost pro použití v automobilových aplikacích – Tento produkt NXP byl kvalifikován pro použití v automobilových aplikacích. Pokud je tento produkt zákazníkem použit při vývoji nebo pro začlenění do produktů nebo služeb (a) používaných v bezpečnostně kritických aplikacích nebo (b) u nichž by selhání mohlo vést k úmrtí, zranění osob nebo vážným fyzickým škodám či škodám na životním prostředí (takové produkty a služby dále označované jako „kritické aplikace“), pak zákazník činí konečná rozhodnutí o návrhu svých produktů a je výhradně odpovědný za dodržování všech právních, regulačních a bezpečnostních požadavků týkajících se jeho produktů, bez ohledu na jakékoli informace nebo podporu, které může společnost NXP poskytnout. Zákazník jako takový přebírá veškerá rizika spojená s použitím jakýchkoli produktů v kritických aplikacích a společnost NXP a její dodavatelé nenesou odpovědnost za žádné takové použití zákazníkem.

V souladu s tím zákazník odškodní a ochrání NXP za jakékoli nároky, závazky, škody a související náklady a výdaje (včetně poplatků za právní zastoupení), které NXP mohou vzniknout v souvislosti se začleněním jakéhokoli produktu zákazníka do kritické aplikace.

Kontrola vývozu — Tento dokument, stejně jako položky zde popsané, mohou podléhat předpisům o kontrole vývozu. Vývoz může vyžadovat předchozí povolení od příslušných orgánů.

Publikace HTML — Jako laskavost poskytujeme verzi HTML tohoto dokumentu, je-li k dispozici. Definitivní informace jsou obsaženy v příslušném dokumentu ve formátu PDF. Pokud existuje nesrovnalost mezi dokumentem HTML a dokumentem PDF, má prioritu dokument PDF.

Překlady — Neanglická (přeložená) verze dokumentu, včetně právních informací v tomto dokumentu, je pouze orientační. V případě jakéhokoli rozporu mezi přeloženou a anglickou verzí má přednost anglická verze.

Zabezpečení — Zákazník chápe, že všechny produkty NXP mohou být předmětem neidentifikovaných zranitelností nebo mohou podporovat zavedené bezpečnostní standardy nebo specifikace se známými omezeními. Zákazník je odpovědný za návrh a provoz svých aplikací a produktů po celou dobu jejich životního cyklu, aby se snížil účinek těchto zranitelností na aplikace a produkty zákazníka. Odpovědnost zákazníka se vztahuje také na další otevřené a/nebo proprietární technologie podporované produkty NXP pro použití v aplikacích zákazníka. NXP nenese žádnou odpovědnost za jakoukoli zranitelnost. Zákazník by měl pravidelně kontrolovat aktualizace zabezpečení z NXP a patřičně je sledovat.

Zákazník si musí vybrat produkty s bezpečnostními prvky, které nejlépe splňují pravidla, předpisy a normy zamýšlené aplikace a učinit konečná rozhodnutí o designu týkající se svých produktů a je výhradně odpovědný za shodu se všemi právními, regulačními a bezpečnostními požadavky týkajícími se jeho produktů, bez ohledu na jakékoli informace nebo podporu, kterou může NXP poskytnout.

NXP má tým pro reakci na bezpečnostní incidenty produktu (PSIRT) (dostupný na adrese PSIRT@nxp.com), která spravuje vyšetřování, hlášení a uvolňování řešení bezpečnostních zranitelností produktů NXP.

NXP BV — NXP BV není provozní společností a nedistribuuje ani neprodává produkty.

ochranné známky

Oznámení: Všechny odkazované značky, názvy produktů, názvy služeb a ochranné známky jsou majetkem příslušných vlastníků.

NXP — slovo a logo jsou ochranné známky společnosti NXP BV

AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Autorská práva, designy a obchodní tajemství. Všechna práva vyhrazena.

Kinetický — je ochranná známka společnosti NXP BV

Uvědomte si prosím, že důležitá upozornění týkající se tohoto dokumentu a zde popsaných produktů byla zahrnuta v části „Právní informace“.

© 2025 NXP BV

Další informace naleznete na adrese: https://www.nxp.com

Všechna práva vyhrazena.

Zpětná vazba dokumentu

Datum vydání: 3. února 2025

Identifikátor dokumentu: UM12212

Dokumenty / zdroje

|

Vývojová sada pro řízení motoru NXP S32K396 [pdfUživatelská příručka S32K396-BGA-DC1, S32K396 289MapBGA, S32K396 Vývojová sada pro řízení motoru, S32K396, Vývojová sada pro řízení motoru, Vývojová sada pro řízení, Vývojová sada |