Lineární technologie DEMONSTRACE OBVOD 1255 16-BIT 25OKSPS ADC

POPIS

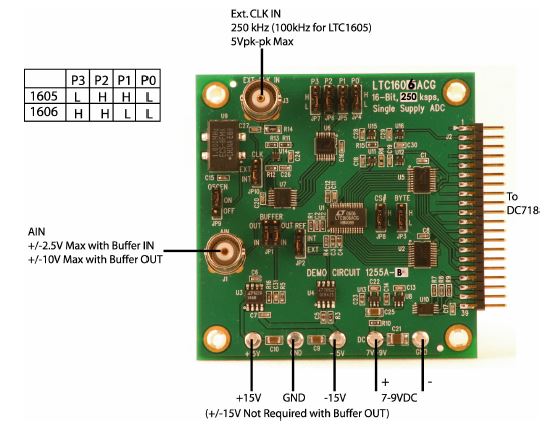

LTC1606 je 250Ksps ADC, který odebírá pouze 75mW z jediného +5V zdroje, zatímco LTC1605 je 100Ksps ADC, který odebírá pouze 55mW z jednoho +5V zdroje. DC1255 může použít kteroukoli část. Následující text odkazuje na LTC1606, ale vztahuje se také na LTC1605 s příslušnými sampúvahy o frekvenci. Demonstrační obvod 1255 poskytuje uživateli prostředek pro vyhodnocení výkonu LTC1605/LTC1606 a je určen k demonstraci doporučeného uzemnění, umístění součástí, směrování a přemostění. Design files pro tuto desku plošných spojů jsou k dispozici. Zavolejte do továrny LTC.

POSTUP RYCHLÉHO STARTU

Připojte DC1255A k DC718B USB High Speed Data Collection Board pomocí konektoru J2. Připojte DC718B k hostitelskému počítači pomocí standardního kabelu USB A/B. Aplikujte 7V-9V DC na svorky 7V-9V a GND. Aplikujte +15V a -15V na označené svorky, pokud má být použita vnitřní vyrovnávací paměť (výchozí). Použijte zdroj signálu s nízkým jitterem na J1. Jako zdroj hodin lze použít buď vestavěné hodiny nebo nízký jitter 250 kHz 10 dBm sinusový nebo obdélníkový do konektoru J3. Všimněte si, že J3 má zakončovací odpor 50• k zemi. Spusťte software QuickEval-II (Pscope.exe verze K51 nebo novější) dodávaný s DC718B nebo si jej stáhněte z www.linear.com.

NASTAVENÍ

DC napájení

DC1255 vyžaduje k napájení 7-9VDC při přibližně 24mA a +/- 15V ampčistič U3. Pokud nepoužíváte U3 (viz propojka JP1), nemusíte poskytovat +/-15V. Napájení 7-9VDC napájí ADC prostřednictvím regulátoru LT1761-5, který poskytuje ochranu proti náhodnému zpětnému předpětí. Podrobnosti o připojení viz obrázek 1.

Zdroj hodin

JP10 (CLK) určuje, zda je DC1255 interně (výchozí) nebo externě taktovaný. Vnitřní hodiny tvoří hodinový oscilátor ECS 1MHz, který je dělen čítačem 74VHC161. Tento oscilátor lze vypnout nastavením JP9 (OSCEN) do polohy OFF. Propojky (JP4-JP7) nastavují dělicí poměr vnitřních hodin pro příslušný ADC (LTC1605 nebo LTC1606). Nastavení propojek viz tabulka na obrázku 1. Pro externí hodiny musíte zajistit nízký jitter 10dBm sinusový nebo obdélníkový do J3. Všimněte si, že J3 má zakončovací odpor 50 proti zemi. Řízení tohoto vstupu pomocí logiky bude obtížné. Pomalé náběžné hrany mohou ohrozit SNR převodníku za přítomnosti vysokýchampvstupní signály vyšší šířky. Demonstrační deska obsahuje obvod detektoru hran. Kompletní softwarová dokumentace je k dispozici v nabídce Nápověda. Aktualizace lze stáhnout z nabídky Nástroje. Pravidelně kontrolujte aktualizace, protože mohou být přidány nové funkce. Software Pscope by měl rozpoznat DC1255A a automaticky se nakonfigurovat. Kliknutím na tlačítko Collect (viz obrázek 2) zahájíte získávání dat. V závislosti na tom, kterou desku dříve používal Pscope, může být nutné stisknout tlačítko Collect podruhé. Tlačítko Shromáždit se poté změní na Pozastavit, na které lze kliknout a zastavit sběr dat. ve formě invertoru (U14) následovaného zpožděním 200 ns, napájejícím spolu s původním zdrojem hodin dvouvstupové hradlo NAND (U7B). Toto vygeneruje aktivní nízký puls na ADC přibližně 200 ns, pokud je nejvyšší čas vyšší než 200 ns. K testování těchto demo desek se obvykle používá 50% pracovní cyklus na 250 kHz. Kratší pulzy pracovního cyklu (aktivní High na J3) lze použít minimálně do 40 ns.

Výstup dat

Paralelní datový výstup z této desky (0V-3.3V), pokud není připojen k DC718, lze získat logickým analyzátorem a následně importovat do tabulkového procesoru nebo matematického balíčku v závislosti na požadované formě digitálního zpracování signálu.

Propojky BYTE a CS#

Demo deska je obvykle dodávána s BYTE (JP3) a CS# (JP8) připojenými k zemi. Pokud zamýšlíte provozovat toto zařízení způsobem, který zahrnuje tyto linky, můžete použít propojky jako prostředek k zavedení těchto signálů z externího zdroje.

Odkaz

JP2 vám umožňuje vybrat jako referenční referenci na čipu nebo externí LT1019A-2.5 (výchozí). Typické specifikace driftu externí reference jsou podobné referenci na čipu, ale LT1019-2.5 má garantovaná maxima.

analogový vstup

Demo deska se dodává s JP1 v poloze ''IN'', v takovém případě je vstup amplifier je v cestě signálu. S JP1 v poloze ''IN'' poskytuje U3 (LT1468) zisk 9dB. To umožní generátoru signálu s výstupní úrovní 2.5 V RMS, aby převedl převodník na plný rozsah. Tento ampliifier nesnižuje SNR nebo zkreslení výkonu převodníku. Vstupní hustota šumu samotného LT1468 je 5 nV/•Hz. V konfigurovaném obvodu je impedance sítě zpětné vazby a ampvstupní šumový proud lifier přispívá k šumovému výkonu; k vytvoření vstupní hustoty šumu 7.44 nV/•Hz. Se ziskem 2.82 to produkuje 17uV RMS šumu v šířce pásma 675 kHz vnucené převodníkem. To je odstup signálu od šumu 112 dB v plném rozsahu. To samozřejmě nelze ověřit na výstupu ADC. S JP1 v poloze ''OUT'' je vstupní impedance na J1 10K•. S JP1 v poloze ''IN'' je vstupní impedance velmi vysoká. Pokud je J1 buzen generátorem určeným k buzení impedance 50•, možná budete chtít použít průchozí terminátor 50•. Pokud má být hodnocen zdroj s vyšší impedancí, uvidíte lepší výsledky s ampli-fir v cestě signálu. Pokud chcete hodnotit amplifikujte v jednotkovém zesílení, přesuňte R5 nebo připájejte rezistor s nízkou hodnotou paralelně s R16. Pokud chcete hodnotit amplifier s vyšším ziskem, můžete snížit hodnotu R5. Pokud použijete velmi kvalitní rezistory, měli byste být schopni zvýšit zisk na 50, než se hladina šumu převodníku znatelně zvýší. A svtagZisk 10 by měl vést k poklesu typického SNR 90 dB na 89.9 dB. A svtagZesílení 50 by mělo poskytnout přibližně 88.7 dB a zisk 100 by dalo přibližně 86 dB SNR. THD se zvýší, ale se ziskem 50 je THD LT1468 stále typicky v rozsahu -90 dB.

Pokud ampLiifier je nakonfigurován pro vysoký zisk, mohou být zjištěny rozdíly zemního potenciálu mezi různými nástroji na vašem stole, aby se vytvořil diferenciální komponent na vstupu do demo desky. K dosažení dobrých výsledků se ziskem 50 může být vyžadována izolace transformátoru.

Sběr dat

Systém používaný pro sběr dat může mít negativní vliv na výkon demo desky, pokud produkuje významný zemní proud skrz demo desku. Tato demonstrační deska je testována ve vlastní režii duplikací FFT grafu zobrazeného v levém dolním rohu stránky 6 datového listu LTC1606. To zahrnuje použití zdroje hodinového signálu 250 kHz s nízkým jitterem pro kódovací hodiny spolu s nízkošumovým sinusovým generátorem s nízkým zkreslením na frekvenci v blízkosti 1 kHz. The amplifier je ''IN'' pro interní test a úroveň vstupního signálu je přibližně -1dBfs. FFT zobrazená v datovém listu je 4096-bodová FFT se vstupní frekvencí přesně 1037.5976 Hz. Tato frekvence je „koherentní“ (vytváří celočíselný počet cyklů základní hodnoty v okně) pro hodinovou frekvenci 250 kHz a prvočíslo cyklů (17 cyklů). Prvočíslo integrálních cyklů vykonává největší počet možných vstupních kódů. Jiné frekvence hodin vyžadují různé vstupní frekvence pro koherentní sampling. Pro výpočet vstupní frekvence f pro dané sampfrekvence fs, počet samples n a prvočíslo m, použijte následující vzorec.

Existuje řada scénářů, které mohou při hodnocení ADC přinést zavádějící výsledky. Jedním z běžných je napájení měniče frekvencí, která je podnásobkem sample rate, a který uplatní pouze malou podmnožinu možných výstupních kódů. Všimněte si také, že DC1255 nemá anti-aliasingový filtr.

Za propojkou JP1 následuje 800kHz dolní propust prvního řádu (R1 a C2). To znatelně nemění bod —3dB převodníku, který je typicky 675 kHz. R1 a C2 tedy netvoří antialiasingový filtr. Pokud ve svém hodnocení požadujete antialiasingový filtr, měl by být obecně umístěn před LT1468 nebo jakýmkoliv externím amplifier v cestě signálu. Pokud máte frekvenční složky, které jsou nad Nyquistovou (1/2 fs) a do a za 675 kHz, složí se zpět do základního pásma DC-125 kHz a stanou se nerozeznatelné od signálů v tomto pásmu.

Pokud nemáte generátor signálu schopný frekvenční přesnosti na úrovni ppm, můžete použít FFT s okénkem ke snížení ''úniku'' nebo šíření základního signálu, abyste získali co nejpřesnější aproximaci výkonových parametrů. Pokud ampPokud je použit zesilovač nebo zdroj hodin se špatným fázovým šumem, okno nezlepší SNR. Zdroj signálu typicky používaný pro domácí testování je B&K 1051. Zdroj interních hodin je dostačující pro většinu aplikací. Stejně jako u každého vysoce výkonného ADC je tato část citlivá na rozložení. Oblast bezprostředně obklopující ADC by měla být použita jako vodítko pro umístění a směrování různých součástí spojených s ADC. Všimněte si také základní roviny použité v uspořádání této desky.

DEMONSTRACE OKRUH 1255

Dokumenty / zdroje

|

Lineární technologie DEMONSTRACE OBVOD 1255 16-BIT 25OKSPS ADC [pdfUživatelská příručka 1255 16-BIT 25OKSPS ADC, DEMONSTRACE OBVOD |