bloky logického pole intel Agilex a moduly adaptivní logiky

Intel® Agilex™ LAB a ALM Overview

Blok logického pole (LAB) se skládá ze základních stavebních bloků známých jako adaptivní logické moduly (ALM). LAB můžete nakonfigurovat tak, aby implementovaly logické funkce, aritmetické funkce a funkce registrů.

Polovinu dostupných LAB v zařízeních Intel® Agilex™ můžete použít jako paměťové LAB (MLAB). Některá zařízení mohou mít vyšší poměr MLAB.

Software Intel Quartus® Prime a další podporované nástroje pro syntézu třetích stran automaticky vybírají vhodný režim pro běžné funkce, jako jsou čítače, sčítačky, odečítače a aritmetické funkce.

Intel Hyperflex™ Core Architecture, Intel Agilex Device Overview

Poskytuje další informace o Hyper-Registers a architektuře jádra Intel Hyperflex™. Hyper-Registers jsou další registry dostupné v každém propojovacím směrovacím segmentu v rámci jádra, včetně směrovacích segmentů připojených k LAB vstupům a výstupům.

Registrace Intel Hyperflex™

Řada zařízení Intel Agilex je založena na architektuře jádra Intel Hyperflex™.

Intel Agilex LAB obsahuje registry Intel Hyperflex a další funkce navržené pro usnadnění přečasování. Registry Intel Hyperflex jsou dostupné v ALM a přenosových řetězcích. Jak je znázorněno na obrázku Intel Agilex ALM Connection Details, registry Intel Hyperflex jsou umístěny na synchronním vynulování a taktování umožňuje vstupům zvýšit nebo snížit zpoždění cesty. Všechny registry Intel Hyperflex lze aktivovat a jsou řízeny softwarem Intel Quartus Prime během přečasování.

Architektura a funkce Intel Agilex LAB a ALM

Následující části popisují LAB a ALM pro zařízení Intel Agilex.

LABORATOŘ

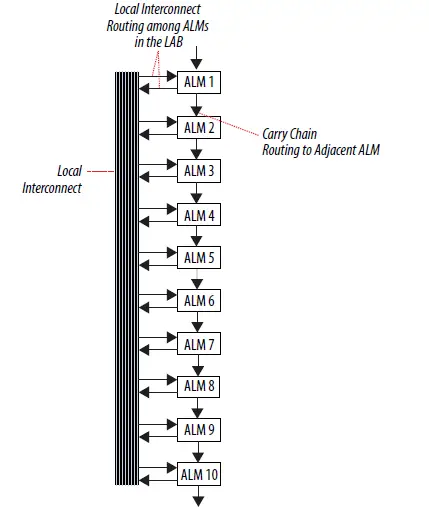

LAB jsou konfigurovatelné logické bloky, které se skládají ze skupiny logických zdrojů. Každý LAB obsahuje vyhrazenou logiku pro řízení řídicích signálů do jeho ALM. MLAB je nadmnožinou LAB a zahrnuje všechny funkce LAB. V každém LAB je celkem 10 ALM, jak je znázorněno na obrázku Intel Agilex LAB a MLAB Structure.

Obrázek 1.

Struktura Intel Agilex LAB a propojení přesview

Tento obrázek ukazuje překročeníview struktury Intel Agilex LAB a MLAB s propojením LAB.

Související informace

Související informace

MLAB na straně 6

MLAB

Každý MLAB podporuje maximálně 640 bitů jednoduché dvouportové SRAM. Každý ALM v MLAB můžete nakonfigurovat jako paměťový blok 32 (hloubka) x 2 (šířka), výsledkem čehož je konfigurace 32 (hloubka) x 20 (šířka) jednoduchého bloku SRAM se dvěma porty.

Obrázek 2.

Struktura Intel Agilex LAB a MLAB Místní a přímé propojení

Místní a přímé propojení

Každá laboratoř může vyřadit 60 výstupů ALM. Část z nich může přímo řídit vstupy LAB, ale jakékoli připojení k jinému řádku nebo sloupci musí používat alespoň jeden univerzální směrovací vodič.

Místní propojení řídí vstupy ALM. Výstupy ALM, stejně jako propojení sloupců a řádků řídí místní propojení.

Obrázek 3. Místní a přímé propojení Intel Agilex LAB  Propojení nosných řetězů

Propojení nosných řetězů

Mezi ALM je vyhrazená přenosová řetězová cesta. Zařízení Intel Agilex obsahují vylepšenou strukturu propojení v laboratořích LAB pro směrování přenosových řetězců pro efektivní aritmetické funkce. Tato spojení ALM-to-ALM obcházejí místní propojení.

Registry Intel Hyperflex jsou přidány do přenosového řetězce, aby umožnily flexibilní přečasování v řetězci laboratoří a kompilátor Intel Quartus Prime se automaticky vylepšuje.tage těchto zdrojů ke zlepšení využití a výkonu.

Obrázek 4. Propojení nosných řetězů Kontrolní signály LAB

Kontrolní signály LAB

V každém řídicím bloku LAB jsou dva zdroje hodin, které generují dvě hodiny LAB (LABCLK[1:0]) a dvě zpožděné hodiny LAB (LABCLK_Phi1[1:0]) pro řízení registrů ALM a Hyper-Registrů v LAB. LAB podporuje dva jedinečné signály pro povolení hodin a další jasné signály pro registry ALM.

Řádkové hodiny LAB [5..0] a místní propojení LAB generují řídicí signály pro celou LAB. Síť hodin s nízkým zkreslením distribuuje globální signály do řádkových hodin [5..0]. Propojení MultiTrack se skládá ze souvislých, výkonově optimalizovaných směrovacích linek různých délek a rychlostí používaných pro efektivitu směrování. Intel Quartus Prime Compiler automaticky směruje kritické cesty návrhu na rychlejší propojení, aby zlepšil výkon návrhu a optimalizoval prostředky zařízení.

Jasné ovládání logiky

Signály pro celou LAB řídí logiku signálu vymazání registru ALM. Registr ALM přímo podporuje synchronní i asynchronní vymazání. Každý LAB podporuje jeden synchronní signál clear a dva asynchronní signály clear.

Zařízení Intel Agilex poskytují resetovací kolík pro celé zařízení (DEV_CLRn), který resetuje všechny registry v zařízení. Pin DEV_CLRn můžete povolit v softwaru Intel Quartus Prime před kompilací. Resetovací signál v celém zařízení potlačí všechny ostatní řídicí signály.

Obrázek 5. Řídicí signály Intel Agilex LAB-Wide

ALM

Následující části pokrývají zdroje ALM, výstup ALM a provozní režimy ALM.

Zdroje ALM

Každý ALM obsahuje řadu zdrojů založených na LUT, které lze rozdělit mezi dvě kombinační adaptivní LUT (ALUT), dvoubitovou plnou sčítačku a čtyři registry.

S až osmi vstupy pro dva kombinační ALUT může jeden ALM implementovat různé kombinace dvou funkcí. Tato přizpůsobivost umožňuje ALM být zcela zpětně kompatibilní se čtyřmi vstupními architekturami LUT. Jeden ALM může také implementovat podmnožinu osmi vstupních funkcí.

Jeden ALM obsahuje čtyři programovatelné registry. Každý registr má následující porty:

- Data v

- Data ven

- Normální LAB hodiny

- Zpožděné hodiny LAB

- Aktivace hodin

- Synchronní jasné

- Asynchronní jasné

Globální signály, piny I/O (GPIO) pro všeobecné použití nebo jakákoli interní logika mohou řídit signál aktivace hodin, hodiny a asynchronní nebo synchronní řídicí signály vymazání registru ALM. Signál povolení hodin má přednost před signálem synchronního resetu.

U kombinačních funkcí jsou registry vynechány a výstup vyhledávací tabulky (LUT) a sčítaček se přivádí přímo na výstupy ALM. K dispozici jsou dva rychlé výstupy pro 6 výstupů LUT a spodních 5 výstupů LUT pro obejití výstupního muxu a připojení k jinému LAB pro nastavení kritické cesty.

Obrázek 6. Blokový diagram vysoké úrovně Intel Agilex ALM

Výstup ALM

Výstup ALM

Obecné směrovací výstupy v každém ALM řídí místní, řádkové a sloupcové směrovací prostředky. Šest výstupů ALM, včetně dvou rychlých výstupních cest, může řídit připojení směrování sloupců, řádků nebo přímé linky.

Výstup LUT, sčítačka nebo registr může řídit výstupy ALM. Jak LUT nebo sčítačka, tak registr ALM mohou vyjíždět z ALM současně.

Sbalení registrů zlepšuje využití zařízení tím, že umožňuje sbalit nesouvisející registr a kombinační logiku do jediného ALM. ALM může také vyřadit registrované a neregistrované verze výstupu LUT nebo sčítačky.

Následující obrázek ukazuje připojení Intel Agilex ALM. V editoru vlastností Intel Quartus Prime Resource Property Editor je celé připojení ALM zjednodušeno. Některá směrování budou směrována interně softwarem Intel Quartus Prime.

Obrázek 7. Podrobnosti o připojení Intel Agilex ALM Provozní režimy ALM

Provozní režimy ALM

Intel Agilex ALM pracuje v kterémkoli z následujících režimů:

- Normální režim

- Rozšířený režim LUT

- Aritmetický režim

Normální režim

Normální režim umožňuje implementovat dvě funkce v jednom Intel Agilex ALM nebo jednu funkci až šesti vstupů.

Až osm datových vstupů z místního propojení LAB je vstupy do kombinační logiky.

ALM může podporovat určité kombinace zcela nezávislých funkcí a různé kombinace funkcí, které mají společné vstupy.

Kompilátor Intel Quartus Prime automaticky vybírá vstupy do LUT. ALM v normálním režimu podporují sbalování registrů.

Následující obrázek ukazuje kombinaci různých vstupních připojení pro režim LUT. Ve vašem návrhu může software Intel Quartus Prime při kompilaci přiřadit různé názvy vstupů.

Obrázek 8. ALM v normálním režimu

Podporovány jsou také kombinace funkcí s menším počtem vstupů, než je uvedeno. Napřample jsou podporovány kombinace funkcí s následujícím počtem vstupů.

- 4 a 3

- 3 a 3

- 3 a 2

- 5 a 2

Pro sbalení dvou 5vstupových funkcí do jednoho ALM musí mít funkce alespoň dva společné vstupy. Společnými vstupy jsou dataa a datab. Kombinace 4vstupové funkce s 5vstupovou funkcí vyžaduje jeden společný vstup (buď dataa nebo datab).

V málo používaném zařízení mohou být funkce, které by mohly být umístěny v jednom ALM, implementovány v samostatných ALM softwarem Intel Quartus Prime, aby bylo dosaženo nejlepšího možného výkonu. Jakmile se zařízení začne plnit, software Intel Quartus Prime automaticky využívá plný potenciál Intel Agilex ALM. Intel Quartus Prime Compiler automaticky vyhledává funkce pomocí společných vstupů nebo zcela nezávislých funkcí, které mají být umístěny do jednoho ALM, aby bylo možné efektivně využívat zdroje zařízení. Kromě toho můžete ručně ovládat využití zdrojů nastavením přiřazení umístění.

Obrázek 9. 6vstupová funkce režimu LUT v normálním režimu

Obrázek 10. 3vstupová funkce režimu LUT v normálním režimu

Obrázek 10. 3vstupová funkce režimu LUT v normálním režimu

data a data b jsou k dispozici pro balení registrů.  Pomocí následujících vstupů můžete implementovat libovolné tři až šest vstupních funkcí:

Pomocí následujících vstupů můžete implementovat libovolné tři až šest vstupních funkcí:

- datae

- datad0

- datac0

- datac1

- datad1

- dataf

- dataa a datab – přičemž dataa a datab jsou sdíleny mezi oběma LUT, aby byla zajištěna flexibilita pro implementaci jiné funkce v každé LUT.

Oba vstupy dataa i datab podporují funkci sbalení registrů. Pokud povolíte funkci sbalování registrů, vstupy dataa i datab nebo jeden ze vstupů obcházejí LUT a přímo se přivádějí do registru, v závislosti na použitém režimu sbaleného registru. Pro zařízení Intel Agilex jsou podporovány následující typy režimů sbaleného registru:

- 5vstupová LUT s 1 zabalenou cestou registru

- 5vstupová LUT se 2 zabalenými cestami registrů

- Dvě 3vstupové LUT se 2 zabalenými cestami registrů

3vstupová LUT se 2 sbalenými cestami registrů je znázorněna na obrázku 3vstupová funkce LUT režimu v normálním režimu. U zařízení Intel Agilex režim 6vstupové LUT nepodporuje funkci sbalení registrů.

Rozšířený režim LUT

Obrázek 11. Podporované funkce s 8 vstupy v režimu Extended LUT

Určité 8vstupové funkce lze implementovat v jediném ALM pomocí všech vstupů LUT:

- datae

- datad0

- datac0

- dataa

- datab

- datac1

- datad1

- dataf

V režimu rozšířené LUT s 8 vstupy je podporován režim sbaleného registru za předpokladu, že sbalený registr sdílí vstup dataa nebo datab s 8vstupovou LUT.

Aritmetický režim

ALM v aritmetickém režimu používá dvě sady dvou 4vstupových LUT spolu se dvěma vyhrazenými úplnými sčítačkami. Vyhrazené sčítačky umožňují LUT provádět předsčítací logiku. Každá sčítačka tedy může přidat výstup dvou 4vstupových funkcí.

Aritmetický režim také nabízí povolení hodin, povolení čítače, synchronní ovládání nahoru a dolů, ovládání přidávání a odečítání a synchronní vymazání.

Volby clear a clock enable jsou signály pro celou LAB, které ovlivňují všechny registry v LAB. Tyto signály můžete jednotlivě zakázat nebo povolit pro každý pár registrů v adaptivní LUT (ALUT). Software Intel Quartus Prime automaticky umístí všechny registry, které počítadlo nepoužívá, do jiných laboratoří.

Obrázek 12. Intel Agilex ALM v aritmetickém režimu

Nosný řetěz

Nosný řetěz

Nosný řetěz poskytuje funkci rychlého přenášení mezi vyhrazenými sčítačkami v aritmetickém režimu.

Funkce 2bitového přenosu v zařízeních Intel Agilex rozděluje zpoždění přenosu přenosových řetězců s ALM. Nosné řetězy mohou začít buď v prvním ALM, nebo v šestém ALM v LAB. Konečný prováděcí signál je směrován do ALM, kde je přiváděn do místního, řádkového nebo sloupcového propojení.

Historie revizí dokumentu pro uživatelskou příručku bloků logického pole Intel Agilex a modulů adaptivní logiky

| Verze dokumentu | Změny |

| 2022.05.24 | Aktualizovaný obrázek: Blokový diagram vysoké úrovně Intel Agilex ALM. |

| 2019.11.14 | Aktualizován popis v části Kontrolní signály LAB. |

| 2019.10.01 |

|

| 2019.04.02 | Počáteční vydání. |

Intel Corporation.

Všechna práva vyhrazena. Intel, logo Intel a další značky Intel jsou ochranné známky společnosti Intel Corporation nebo jejích dceřiných společností. Společnost Intel zaručuje výkon svých FPGA a polovodičových produktů podle aktuálních specifikací v souladu se standardní zárukou společnosti Intel, ale vyhrazuje si právo provádět změny jakýchkoli produktů a služeb kdykoli bez upozornění. Společnost Intel nepřebírá žádnou odpovědnost nebo závazky vyplývající z aplikace nebo použití jakýchkoli informací, produktů nebo služeb zde popsaných, s výjimkou případů, kdy je společnost Intel výslovně písemně odsouhlasena. Zákazníkům společnosti Intel se doporučuje získat nejnovější verzi specifikací zařízení dříve, než se budou spoléhat na jakékoli zveřejněné informace a než zadají objednávky na produkty nebo služby.

*Jiná jména a značky mohou být nárokovány jako vlastnictví jiných.

ISO

9001:2015

Registrovaný

Dokumenty / zdroje

|

bloky logického pole intel Agilex a moduly adaptivní logiky [pdfUživatelská příručka Bloky logického pole a adaptivní logické moduly Agilex, Agilex, bloky logického pole a adaptivní logické moduly, bloky pole a adaptivní logické moduly, moduly adaptivní logiky, logické moduly |